ความรู้ที่ได้รับ

โดยหลักแล้ว digital circuit มีด้วยกัน 2 แบบคือ

1. Combiration : Input และ Output สามารถคำนวณได้จากการใช้ Truth table มีความแน่นอน2. Sequential : การที่จะรู้ว่า Output จะออกมาเป็นเช่นไรขึ้นอยู่กับ state ก่อนว่า Output แบบใด Input แบบใด และขึ้นอยู่กับ Input ปัจจุบันด้วย สามารถนำไปประยุกต์ใช้เกี่ยวกับ memory และ counter ได้

- พูดถึง basic ของ Combiration ว่าต้องเป็น logic gate ดังนั้นถ้าพูดถึง Sequential เราต้องมองหา Flip-Flop เราจะมาดูกันว่ามันคืออะไร

Flip-Flop

=> อันที่จริงก็คือ logic gate นี่ละเพียงแต่ถูกต่อให้เกิด Truth table ที่ไม่แน่นอน และมีความสามารถในการ memory Output หรือ Input state ก่อนได้เราสนใจ Flip-Flop 4 ประเภทคือ

1. RS Flip - Flop => มีด้วยกัน 4 state ตาม Truth table ไล่ทำความเข้าใจทีละ state

- S เป็น logic 0 และ R เป็น logic 0 มันจะ No change ก็คือ hold วงจรไว้ที่ Output state ก่อนหน้านั่นเอง

- S เป็น logic 0 และ R เป็น logic 1 หรือ S เป็น logic 1 และ R เป็น logic 0 อันนี้จะเป็น Output ที่แน่นอน ตายตัว

- S เป็น logic 1 และ R เป็น logic 1 อันนี้ต้องบอกว่าเป็น state ที่ไม่สามารถประเมินได้ หรือ Undefined เราไม่รู้ว่าจะเกิดอะไรขึ้น ซึ่งจริงๆแล้วมันจะทำให้ทั้ง Q และ Q' ออกเป็น logic 0 ดังนั้นเราจะไม่นำเอามาใช้

2. JK Flip - Flop => อันนี้เป็น Flip-Flop ที่พัฒนามาจาก RS เนื่องจากเราไม่ต้องการ state "undefined" ดังนั้นความแตกต่างอย่างแรกคือ มีการต่อ NAND Gate เพิ่มเข้ามา 2 ตัว เพื่อเปลี่ยน state undefined ที่ไม่ต้องการ ให้กลายเป็น Toggle แทน ในตอนที่ S เป็น logic 1 และ R เป็น logic 1

- หลักการทำงานเหมือนกับ RS flip-flop แต่ว่า บาง IC จะมีขา Reset แยกต่างหากมาด้วย อย่าง IC ที่อาจารย์นำมาให้ใช้ทดลอง ถ้ามีขา Reset หมายความว่า ให้ logic 0 ที่ Reset เมื่อไหร่ Output จะถูก Reset กลับไปเป็นค่าตามที่โรงงานผลิตออกมา

- เมื่อเราทำให้ J เป็น logic 0 และ K เป็น logic 1 หรือ J เป็น logic 1 และ K เป็น logic 0 แล้ว เราต้องกดปุ่ม Clock เพื่อบันทึกค่าให้ Output แสดงออกมา ไม่เช่นนั้น ต่อให้เราสลับ switch แค่ไหน ก็ไม่ทำให้ Output เปลี่ยนไป

- JK flip - flop นั้นก็มี state hold เหมือนกับ RS เมื่อเราให้ J เป็น logic 0 และ K เป็น logic 0 แม้ว่าเราจะกด Clock อย่างไร ก็จะไม่เกิดผลกับ Output เพราะ Clock จะดึง Output ของ state ก่อนมาแสดงวนไปเรื่อยๆ

*Toggle การที่เมื่อ Q เป็นlogic 0 พอ Toggle 1 ครั้ง จะสลับให้ Q เป็น logic 1

3. T-Type Flip-Flop => หมายถึง Flip-Flop ที่ถูกใช้ในการสร้าง Counter

ลักษณะการทำงาน นำขา J และ ขา K ของ JK Flip-Flop มาต่อเข้าหากันเรียกว่าขา T เมื่อเราใส่ T เป็นแบบใด และ ขึ้นอยู่กับ Output ครั้งก่อนหน้าด้วย

- Output ครั้งก่อนเป็น 0 Input T เป็น 0 Output ปัจจุบันจะเป็น 0

- Output ครั้งก่อนเป็น 0 Input T เป็น 1 Output ปัจจุบันจะเป็น 1

เราสามารถแบ่ง Counter ออกได้ 2 รูปแบบคือ

1. Asynchronous Counters => แยกขา Clock ของ JK Flip-Flop เป็นของใครของมัน ไม่ได้ต่อร่วมกัน- ทำให้เกิดการ Delay เวลาเปลี่ยน State จะทำงานช้ากว่า Synchronous

- สร้างได้ง่าย

- ความถี่ต่ำกว่า Synchronous Counter แน่อน

2.Synchronous Counter => ต่อขา Clock ของ JK Flip-Flop ไว้ร่วมกัน

- ต่อได้ยาก ต้องมีการคำนวณว่าต้องเพิ่ม Logic gate แบบใด ต่อกันแบบไหนเพื่อให้ได้วงจรที่ ทำงานได้ตามต้องการ

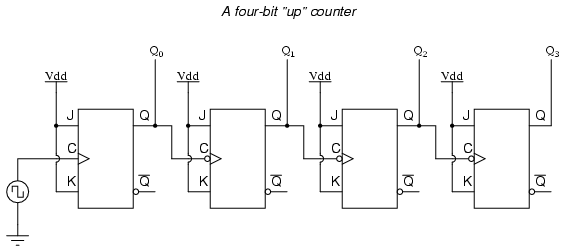

จากหลักการที่กล่าวมาข้างต้นเรานำมาสร้างเป็นวงจรAsynchronous Counter ดังรูป

หลักการทำงานของวงจรคือ มี Output ทั้งหมด 4 ค่าคือ Q0 - Q3 signal ที่ส่งเข้าไปจะเริ่มจาก Clock ส่งหนึ่งครั้ง ดูที่ขอบขาขึ้น จะมีผลกับ Q0 ทำอย่างนี้ไล่ไปตั้งแต่ LSB ถึง MSB เราจะได้วงจรที่สามารถ Counter ค่าได้ ขึ้นอยู่กับ Clock Pulses ที่ส่งมาว่ากี่ครั้ง

4. D-Type Flip - Flop => หมายถึง Flip-Flop ที่ถูกใช้ในการสร้าง Shift Register

ลักษณะการทำงาน

- เมื่อขา Clock เป็น 0 ไม่ว่าขา D จะเป็นอะไรก็ตาม Q และ Q' จะขึ้นอยู่กับ Output state ก่อนหน้า

- เมื่อขา Clock เป็น logic 1 จะมี 2 กรณี

- ขา D logic 0 : Q จะ Output logic 0

- ขา D logic 1 : Q จะ Output logic 1

Shift Register

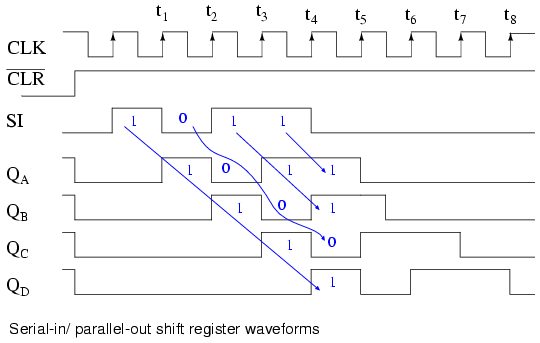

Shift Register หมายถึง การเลื่อน หลักการคือเมื่อเราต้องการส่งข้อมูลอย่างเช่น 1011 อย่างในภาพจะเป็น Input แบบSerial Output แบบ Parallel จะเห็นได้ว่าเราต้องกด Clock ทั้งหมด 4 ครั้งเพื่อให้ข้อมูลเราเข้ามาครบ 4 bit (clock ละ 1 bit) เพื่อให้ข้อมูลเข้าสู่ IC ครบ เป็นต้น หลักการนี้เราใช้เพื่อสร้างความสเถียรให้กับ Signal ที่เราจะนำไปใช้ต่อ หรือว่า ต้องการ Memory ค่าบางค่า เพื่อนำไปคำนวณก็ได้

มีด้วยกัน 4 แบบคือ

- • Serial-in to Parallel-out (SIPO)

- • Serial-in to Serial-out (SISO)

- • Parallel-in to Serial-out (PISO)

- • Parallel-in to Parallel-out (PIPO)

ปัญหาที่พบ

- เราต้องดูให้ดีว่า counter circuits ที่เรานำมาต่อนั้น มี buffer หรือไม่ การมี buffer หรือ นิเสธ หมายถึง ต้องให้ logic 0 ที่ขานั้น วงจรจึงจะทำงาน

- เมื่อเราต่อวงจรจริง สิ่งที่มักผิดพลาดคือการอ่าน datasheet ได้ไม่ดีพอ เนื่องจาก datasheet มีทุกอย่างอยู่แล้ว ถ้าเราสามารถทำความเข้าใจได้อย่างถ่องแท้ จะทำให้เรานำอุปกรณ์นั้นๆไปใช้งานได้อย่างมีคุณภาพและเหมาะสมที่สุด

- ไม่จำเป็นที่ IC ทุกตัวที่เป็น JK Flip-Flop จะต้องมีขา Reset เหมือนกับ IC ที่เราใช้ในการทดลอง

- การที่เราจะload Input แบบ Parallel เข้าไปใน IC นั้นต้องทำให้ขา PE เป็น logic 0 ก่อนแล้วจึงกด Clock 1 ครั้ง เพื่อ upload เปลี่ยนขา PE มาเป็น logic 1 แล้วกด Clock 8 ครั้งเพื่อให้ Output ออกมาเป็น Serial

- ขา CE ต้องเป็น logic 1 เสมอ เพื่อให้ CP ทำงาน ถ้าขา CE เป็น logic 0 ไม่ว่าขา CP จะเป็นอย่างไรก็จะไม่มีผล

อ้างอิง

http://sub.allaboutcircuits.com/images/04353.pnghttp://qph.is.quoracdn.net/main-qimg-8d6bb2ecf259a4d1d876de7b7c30ae22?convert_to_webp=truehttps://upload.wikimedia.org/wikipedia/commons/f/ff/JK-FlipFlop_(4-NAND).PNG

http://worldclassprogramme.com/images/RS-Flip-Flop.gif

http://worldclassprogramme.com/images/D-FlipFlop.gif

http://electronicspost.com/wp-content/uploads/2015/05/14.png

http://www.learnabout-electronics.org/Digital/images/register-SISO.gif

http://www.ee.usyd.edu.au/tutorials/digital_tutorial/part2/pics/regist05.jpg

http://fourier.eng.hmc.edu/e85_old/lectures/figures/T_flipflop.gif

http://www.ee.surrey.ac.uk/Projects/CAL/seq-switching/Graphics/operT.gif

http://www.ibiblio.org/kuphaldt/electricCircuits/Digital/04348.png

http://sub.allaboutcircuits.com/images/04347.png

http://www.electronics-tutorials.ws/counter/count_1.html

http://www.ubooks.pub/Books/B0/E77R7385/MAIN/images/04349.png

ไม่มีความคิดเห็น:

แสดงความคิดเห็น