ความรู้ที่ได้รับ

การ บวก / ลบ เลขฐาน 2 ทาง math

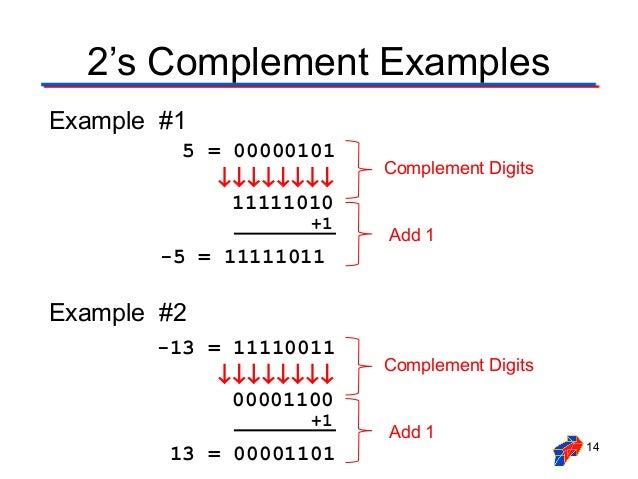

- การทำ 2's Compliment เพื่อให้ได้ค่าติดลบ ของเลขฐาน 2 มีสอง ขั้นตอนขั้นแรก : 1's Compliment คือการแปลง 0 เป็น 1 , แปลง 1 เป็น 0

ขั้นสอง : +1 เพิ่มเข้าไป เพื่อให้ได้ค่าติดลบของตัวเลขตั้งต้น

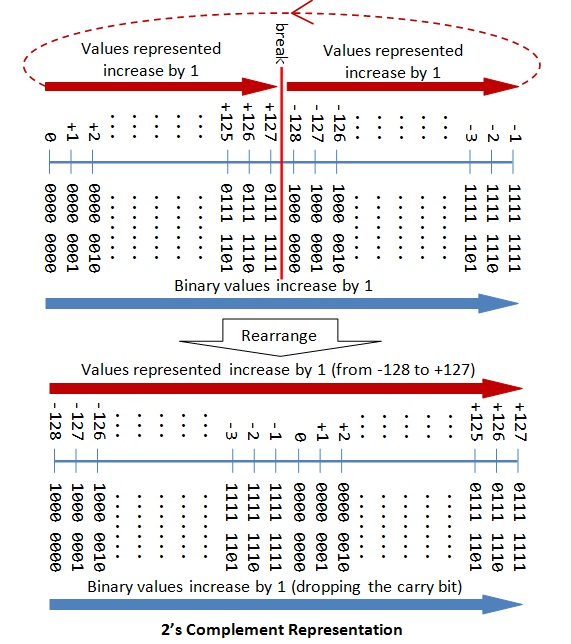

- standard Compliment คือ ค่าที่ช่วง data range เท่ากับ unsign long data แต่ว่า จะมี data ที่ติดลบอยู่ด้วยเช่นถ้าเป็น 8 bit จะมีdata ตั้งแต่ -128 ถึง 127 เป็นต้น

- ค่า maximum ของdata แต่ละบิต คิดจาก 2^n -1 เช่น 8 bit ก็จะมีค่าdata สูงสุดอยู่ที่ 256-1 = 255

- MSB : bitที่มีค่าประจำหลักมากที่สุด เวลาแปลงค่าจะให้ตัวนี้นี่แหละที่ติดลบตัวเดียว ในถ้า standard Compliment MSB เป็น 0 แสดงว่าเป็นdata ค่า + แต่ถ้า MSB เป็น 1 แสดงว่าเป็น data ค่า -

- LSB : bit ที่มีค่าประจำหลักต่ำที่สุด

- ห้าม ทำการบวกค่าdata ที่มีฐานไม่เท่ากัน เด็ดขาด เพราะว่ามันจะทำให้ได้ผลลัพธ์ที่ผิดพลาด

- ผลลัพธ์ที่ได้จากการ + สมมุติว่าเป็นเลขฐาน2 4 bit บวกกัน ก็ต้องได้ 4 bit ถ้าเกิดว่าผลลัพธ์มันเกินต้องตัดทิ้งให้ bit เท่ากับตัวdataตั้งต้นที่นำมาบวก

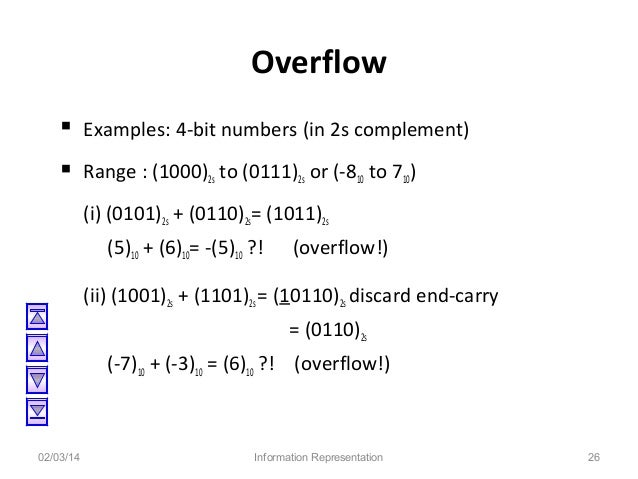

-การที่เป็น standard Compliment มีข้อควรระวังเรียกว่า "Overflow" มันคือการที่ค่าผลลัพธ์จริงเกินจำนวน bit ที่สามารถแสดงได้ ทำให้ผลลัพธ์ที่เราเห็นนั้นผิดพลาดไปจากความเป็นจริง

- วิธี Detect Overflow จากทฤษฎีที่ว่า

data ค่าบวก สองตัว + กันต้องได้ผลลัพธ์เป็น +

data ค่าลบ สองตัว + กันต้องได้ผลลัพธ์เป็น -

*ดังนั้นให้ดูค่าของ MSB ของผลลัพธ์ ถ้าMSB 2 ค่าที่นำมาบวกกันเป็น 0 ผลลัพธ์ต้องมี MSB เป็น 0 ด้วย แต่ถ้า MSB ของผลลัพธ์ ถ้าMSB 2 ค่าที่นำมาบวกกันเป็น 1 ผลลัพธ์ต้องมี MSB เป็น 1 ไม่เช่นนั้นแปลว่าเกิด "Overflow" !!

ส่วนถ้าตัวนึงเป็นdataค่า - , อีกตัวเป็น data ค่า + แล้วนำมาบวกกัน จะไม่เกิด Overflow แน่นอนเพราะค่าลดลง

การต่อวงจร digital บวก / ลบเลขฐาน2

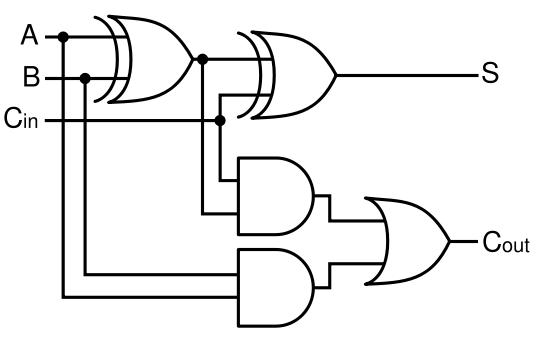

- Half-adder : การต่อ logic gate เพื่อให้สามารถบวกเลขฐาน2 ได้ขนาด 1 bit มีข้อเสียคือไม่สามารถคำนวณตัวทดได้

- จากข้อเสียของ "Half Adder" ทำให้เกิดการต่อแบบ "Full Adder" ซึ่งก็คือการนำ half adder ต่อกันสองชุด เพื่อให้สามารถบวกเลข 1 bit และ คำนวณตัวทด(Carry)จากตัวก่อนได้ ได้อย่างสมบูรณ์เมื่อเทียบกับทฤษฎีทางคณิตศาสตร์

ปัญหาที่พบเจอใน class

ทั้งนี้การต่อแบบ Half Adder หรือ Full Adder ไม่สามารถ ลบเลขฐาน 2 ได้ ดังนั้นจึงต้องออกแบบวงจรแบบใหม่ ที่ประกอบขึ้นจาก วงจรFull Adder ที่ทำงานกับ XOR gate กลายเป็นวงจรที่ + หรือ - เลขได้จากขา OP ที่ต่ออยู่กับ ขา A0,A1,A2,A3

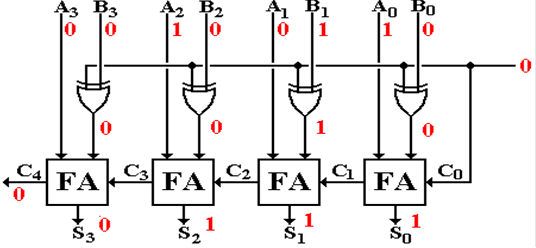

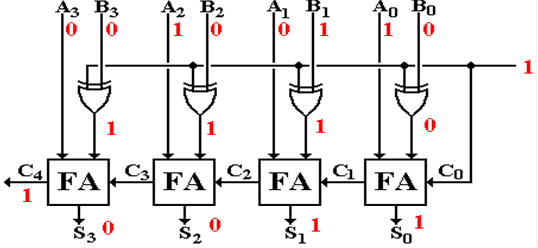

ตัวอย่างการทำงานของวงจรบวก/ลบเลขฐาน

เมื่อ OP เป็น logic 0

เมื่อ OP เป็น logic 1

ปล. ภายในวงจรนี้เราสามารถ Check การ Overflow ได้ด้วย จากการต่อ OR gate เพิ่มเข้าไป 1ตัวให้ขา A เชื่อมกับ C3 และ ขา B เชื่อมกับ C4 เราจะเรียกมันว่า "ขา Overflow" ถ้า logic เป็น 1 แปลว่า เกิดการ Overflow !!

ปัญหาที่พบ

- การต่อวงจรจาก Schematic มีความยากจากการที่เราต้องดูขาของ IC ที่เราหยิบมาด้วย เนื่องจากการเรียงขาไม่ได้เหมือนกันทุกตัว และแต่ละตัวก็มีคุณสมบัติที่ต่างกัน ต่อให้เป็น Gate ชนิดเดียวกัน

-เวลาคำนวณต้อง check ให้แน่ใจก่อนว่า data ที่เราต้องการคำนวณจะอยู่ในช่วงไม่เกินกับที่วงจรของเรารองรับได้ไม่งั้นจะเกิด Overflow

- มักจะมีคนลืมว่าการนำเลขฐานสองมาบวกกัน ต้องเป็น bit ที่เท่ากันเท่านั้น ไม่งั้นค่าจะคลาดเคลื่อนจากความเป็นจริง

- จากการต่อจริงพบว่า สายไฟที่มากและซับซ้อนดังรูปทำให้เวลาผู้อื่นที่ไม่ใช่คนต่อวงจรมาไล่วงจร จะงง และสับสนได้ เป็นการยากที่จะ debug ให้กับเพื่อน หรือคนที่ขอความช่วยเหลือ

อ้างอิง

http://goo.gl/BJqz3i

http://goo.gl/MFIduY

http://goo.gl/o69JpM

ไม่มีความคิดเห็น:

แสดงความคิดเห็น